10

### ♣ 연구책임자

신재생에너지연구소 차세대전지원천기술센터 오준호

한국에너지기술연구원

기술사업화실

042-860-3384

kier-tlo@kier.re.kr

▼ TEL

E-mail

# 화학기상증착법을 이용한 고품질 저비용 에피탁시 실리콘 기판 제조 기술

기존 실리콘 웨이퍼 제작 공정은 고온 Cz성장한 실리콘 잉곳을 절단 가공하여 생산하며, 고온공정비용 및 원재료 절단손실 등의 원가상승 요인을 제거하기 어려움. 이와 달리, 본 기술에서는 태양광 및 광다이오드 등 반도체산업에 사용되는 다양한 스펙의 실리콘기판을 가스반응을 통하여 gas-to-wafer 저비용으로 제조하는 혁신적인 기술.

### ○ 기술의 구성도/개념도

### ○ 기술의 주요 내용 및 특징

- 실리콘 웨이퍼의 단가는 태양광 및 광다이오드 등의 기타 반도체 소자의 제조원가에 직결되기 때문에 태양광 및 반도체 소자용 웨이퍼 제작 세계 선도업체는(예: 중국 Longi) 실리콘 웨이퍼의 비용절감을 위해 전사적인 투자 진행중

- 본 기술은 결정질 실리콘 웨이퍼를 저비용으로 성장하는 기술로서 태양광 뿐 아니라 광다이오드 등의 반도체. LED 및 디스플레이 등의 고부가가치 산업에 파급력이 상당함

- 에피택시 실리콘 웨이퍼 제조는 모체기판에 에피택시 웨이퍼를 성장하고, 성장한 에피택시 웨이퍼를 모체기판으로부터 분리하는 분리공정의 두 가지 핵심기술로 구성됨

- 이 중 에피택시 성장법은 업계전반의 기술적 성숙도가 상향 평준화되어있으나, 분리공정 기술이 아직 성숙되지 않았고, 에피 성장온도가 1000도이상으로써 매우 고온임

### ○ 기술의 적용처

| 응용분야                | 적용제품                                          |  |  |

|---------------------|-----------------------------------------------|--|--|

| 저저항 solar wafer제조   | 실리콘 태양전지용 p/n형 웨이퍼                            |  |  |

| 고저항 실리콘 wafer제조     | 실리콘 광다이오드/방사선센서/<br>photonics                 |  |  |

| 고품질/고순도 실리콘 wafer제조 | SOI웨이퍼, 메모리/비메모리반도체/<br>전력반도체 제작용             |  |  |

| Heteroepitaxy 기판제조  | GaN on Si, SiC on Si 등<br>이종소자integration 구현용 |  |  |

○ 기술의 비교우위성/ 기존 기술 대비 차별성

기존 기술

- 웨이퍼 제작을 위한 Cz잉곳을 1600도의 고온에서 성장함

- · 상압CVD 에피탁시 성장온도는 1000도에 육박함

- 분리막 제작을 위해 전기화학적으로 모체기판을 식각하여 모체기판 소모 발생

본기술

- 본기술은 Cz 및 상압CVD대비 현저히 낮은 공정온도에서 gas-to-wafer공정을 통하여 에피탁시 실리콘 기판 제조 가능

- · 본기술은 모체기판 위에 dual-functional 분리층을 플라즈마CVD를 통하여 성장하므로, 모체기판이 소모되지 않아, 모체기판 반영구적 사용가능

○ 실험 및 실증 데이터

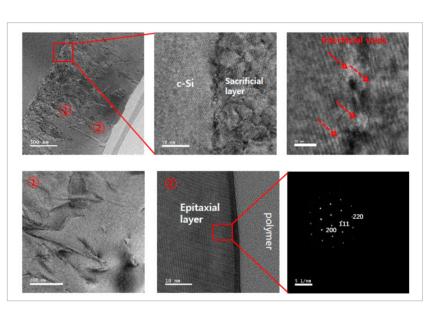

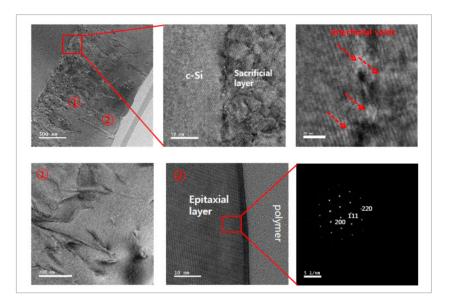

>>> dual-functional 다공성 분리층 상부에 플라즈마CVD법을 이용하여 에피탁시 기판 제작을 하였으며, HRTEM분석(측정용 샘플두께: ~2um)을 통해 기판내부의 결정이 단결정임을 확인함

○ 기술의 성숙도

지식재산권 현황

## I 시작품 I I 기초연구 I 실험

[TRL 3: 실험실 규모의 기본성능 검증]

~ [TRL 4: 실험실 규모의 소재/부품/시스템 핵심성능 평가]

| 순번 | 발명의 명칭                                                  | 출원번호                | 출원일자       | 등록번호                | 등록일자       |

|----|---------------------------------------------------------|---------------------|------------|---------------------|------------|

| 1  | 적층구조 박막 제조방법, 이에 의해 제조된 적층구조<br>박막 및 이를 이용한 반도체 소자 제조방법 | 10-2016-<br>0132676 | 2016,10,13 | 10-1946570-<br>0000 | 2018.11.09 |

| 2  | 고저항 에피탁시 기판을 이용한 반도체 수광 소자 및<br>이를 제조하는 방법              | 10-2018-<br>0142842 | 2018,11,19 | -                   | -          |

10

### Principal researcher

Ulsan Advanced Energy Technology R&D Center of the New and Renewable Energy Institute

Oh Joon-Ho

Inquiries

Research

042-860-3384

kier-tlo@kier.re.kr

**L** Tel

E-mail

Business Development Team of the Korea

Institute of Energy

## Manufacturing Technology of High-quality, Low-cost Epitaxy Silicon Substrates Using a Chemical Vapor Deposition Method

In the existing method, silicon wafers are manufactured by cutting and processing CZ method-based silicon ingots formed at a high temperature, and thus additional process costs are incurred, such as high-temperature process costs and costs from the loss of raw materials during the cutting process. In contrast, the present technology is an innovative gas-to-wafer method that can produce silicon substrates of various specifications, such as PV and optical

diodes, which are widely used in the semiconductor industry.

### Structural Diagram/Conceptual Diagram

### Description and Characteristics of Technology

- Given that the unit price of a wafer directly affects the production cost of semiconductor devices, such as PV and optical diodes, leading global producers of wafers for PV and semiconductor devices (e.g., Longi in China) are making investments to reduce the manufacturing cost of a silicon wafer.

- This technology allows the production of crystalline silicon wafers at low costs, thus posing a significant impact on high value-added industries, such as PV, optical diode, and other semiconductor fields as well as LED and display industries.

- The manufacturing process of an epitaxy silicon wafer is composed of two core technologies: one in which an epitaxy wafer is grown on a mother substrate and the other in which the grown epitaxy wafer is detached from a mother substrate.

- Here, the maturity level of the epitaxy growth technology has been set high across the board, but the separation process technology has yet to be matured, and the epitaxy growth temperature is very high at over 1000°C.

### Scope of Application

| Application Fields                                           | Products                                                                       |

|--------------------------------------------------------------|--------------------------------------------------------------------------------|

| Manufacturing of low-resistance solar wafers                 | p/n type wafers for silicon solar cells                                        |

| Manufacturing of high-resistance silicon wafers              | Silicon optical diodes / radiation sensors / photonics                         |

| Manufacturing of high-quality/<br>high-purity silicon wafers | SOI wafers for memory/non-memory/<br>power electronics                         |

| Manufacturing of heteroepitaxy substrates                    | Products for heterogeneous device integration, such as GaN on Si and SiC on Si |

Comparative advantages of technology / Differentiation

Experimental

data

and empirical

\* The epitaxy growth temperature for APCVD processes is as high as 1000°C.

\* Parent substrates need to be electrochemical.

Parent substrates need to be electrochemically etched to form a separation membrane, and thus mother substrates are somewhat wasted.

Conventional Technology

• Cz ingots for wafer manufacturing are formed at

a high temperature, i.e., 1600°C.

#### Present Technology

- Using the present technology, it is possible to manufacture epitaxial silicon substrates at a much lower temperature through the gas-towafer process, when compared to Cz and APCVD processes.

- A dual-functional separation membrane is grown on a mother substrate through plasma CVD, and therefore mother substrates are not wasted and thus can be used semi-permanently.

>>> An epitaxy substrate was manufactured on top of the dual-functional porous separation membrane through plasma CVD, and the HRTEM analysis confirmed that the crystals within the substrate were single crystals.

Maturity level of technology

Current status of intellectual property rights

## | Basic Research | Experiment | Prototype | Turning into

[TRL 3: Lab-scale basic performance verification]

~ [TRL 4: Key performance evaluation of lab-scale materials/components/systems]

| No. | Title of Invention                                                                                                                        | Application<br>Number | Application<br>Date | Number Number       | Registration<br>Date |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------|---------------------|----------------------|

| 1   | Fabrication method of multilayer film, and multilayer film, and semiconductor device using thereof                                        | 10-2016-<br>0132676   | 2016.10.13          | 10-1946570-<br>0000 | 2018.11.09           |

| 2   | Semiconductor light receiving devices using high-<br>resistance epitaxy substrates and method of<br>fabricating the same                  | 10-2018-<br>0142842   | 2018.11.19          | -                   | -                    |

| 3   | Method and apparatus for fabricating semiconductor device using high resistance epitaxial growth and semiconductor device made therefrom. | 10-2019-<br>0070242   | 2019.06.13          | -                   | -                    |